There is an instruction memory 32 x 32.This module supposed to outputs only the wanted instruction from memory. Zeroextend_1bit ZE1_3 (wr1, (posedge clk) begin Zeroextend_1bit ZE1_2 (rr2, read_reg_2) Zeroextend_1bit ZE1_1 (rr1, read_reg_1) Input signal_reg_write, PC_write_enable ,clk Output reg read_data_1, read_data_2 ,PC_read module mips_registers( read_data_1, read_data_2, write_data, read_reg_1, read_reg_2, write_reg, signal_reg_write, clk ,PC_read, PC_write ,PC_write_enable)

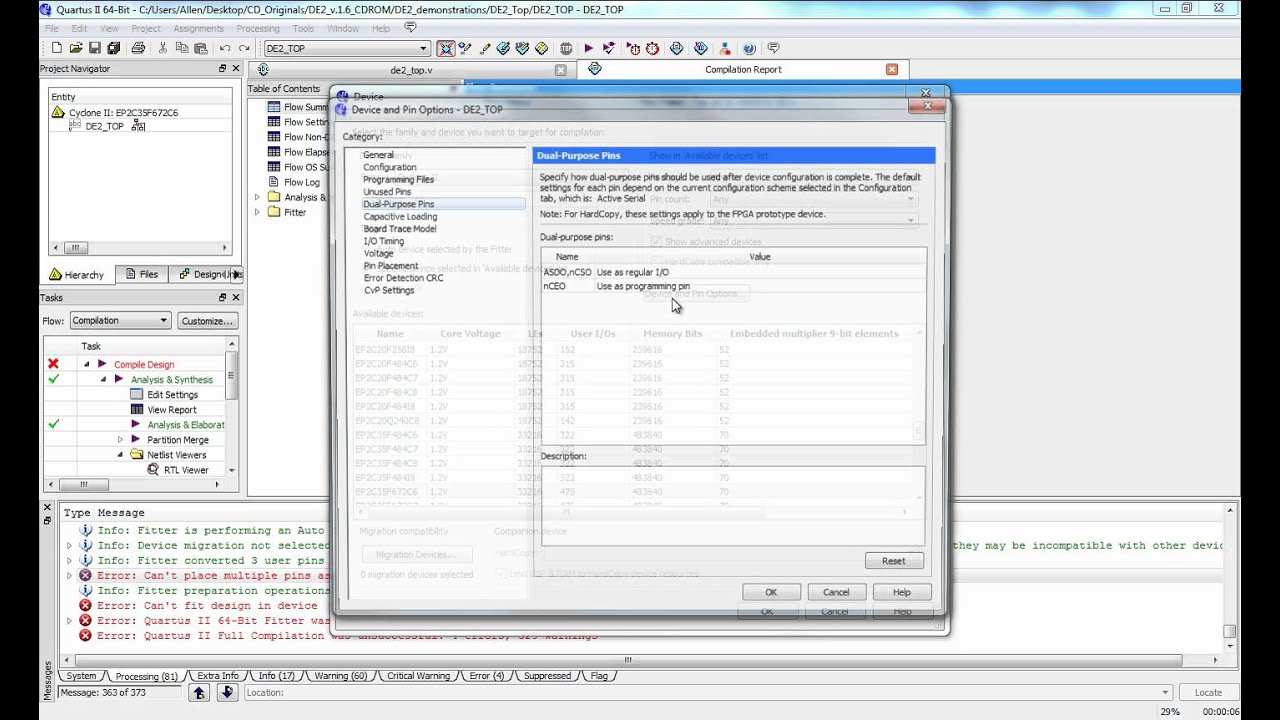

Altera quartus ii output pins stuck at vcc or gnd 32 bit#

There is a file contains 32 bit registers' data and the PC counter.This module supposed to do the i/o operations with it. sw means = select_IJtypeselect_IJtypeselect_IJtype'Īnd AND11 ( data_write_enable, t20, t19) ĭata_memory DM1 (tempr2, result, data_address, data_write_enable, clk) ĮDIT : I added the modules which takes clock signal: Mips_registers MR2 ( tempr0, tempr1, result, instruction, instruction, result_register, write_enable, clk ,tr4, PC_new, 1'b1)

Mux21_1bit M5 (result_register, instruction, instruction ,t18) Mux21_1bit M4 (result_register, instruction, instruction ,t18) Mux21_1bit M3 (result_register, instruction, instruction ,t18) Mux21_1bit M2 (result_register, instruction, instruction ,t18)

Mux21_1bit M1 (result_register, instruction, instruction ,t18) Or OR1 (t17, select_IJtype, select_IJtype) select_IJtype+select_IJtype+select_IJtype If below expression is equal to 1, it means the instruction is I or J type. $display("opcode = %6b, rs = %5b, rt = %5b, rd= %5b, immediate = %16b, address = %26b ,funct = %6b \n",instr, instr, instr, instr, instr, instr ,instr ) Warning (15610): No output dependent on input pin "clk" Warning (21074): Design contains 1 input pin(s) that do not drive logic Warning (13024): Output pins are stuck at VCC or GND Warning (10858): Verilog HDL warning at instruction_memory.v(7): object instructions used but never assigned. So what is the common reasons of these warnings? Any ideas to solve ? I think that the first warning's cause is I did not write anything to instruction memory so you can ignore it. I suppose that it is related to clk signal. Also my main module's outputs are stuck at VCC/GND. The clk is the input of my main module and it says it does not effect any outputs. I am trying to implement a single cycle MIPS processor via Quartus 2 and faced with these warnings.

0 kommentar(er)

0 kommentar(er)